Тепер ви підписані на

Помилка підписки на користувача.

Цей користувач не дозволяє слідувати за ним.

Ви вже слідуєте за цим користувачем.

Ваш членський план дозволяє мати не більше 0 підписок. Покращити рівень членства можна тут.

Успішно відписалися від

Помилка під час скасування підписки на користувача.

Ви успішно рекомендували

Помилка рекомендування користувача.

Щось пішло не так. Будь ласка, оновіть сторінку та повторіть спробу.

Електронну адресу успішно верифіковано.

singapore,

singapore

Зараз тут 3:52 пп

На сайті з серпня 10, 2014

30

Рекомендацій(-ії)

Loi L.

@loi09dt1

6,9

6,9

84%

84%

singapore,

singapore

99%

Завершених робіт

93%

В межах бюджету

97%

Вчасно

14%

Рейтинг повторного найняття

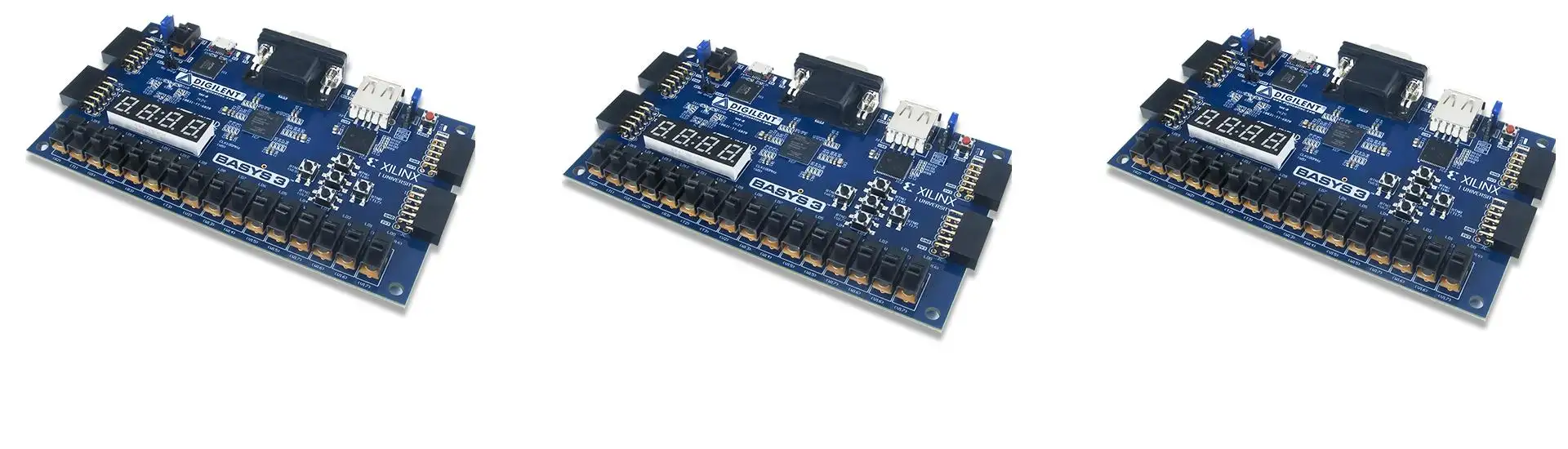

FPGA/Verilog/VHDL Expert

Зв'яжіться з Loi L. щодо вашої роботи

Авторизуйтесь, щоб обговорити деталі в чаті.

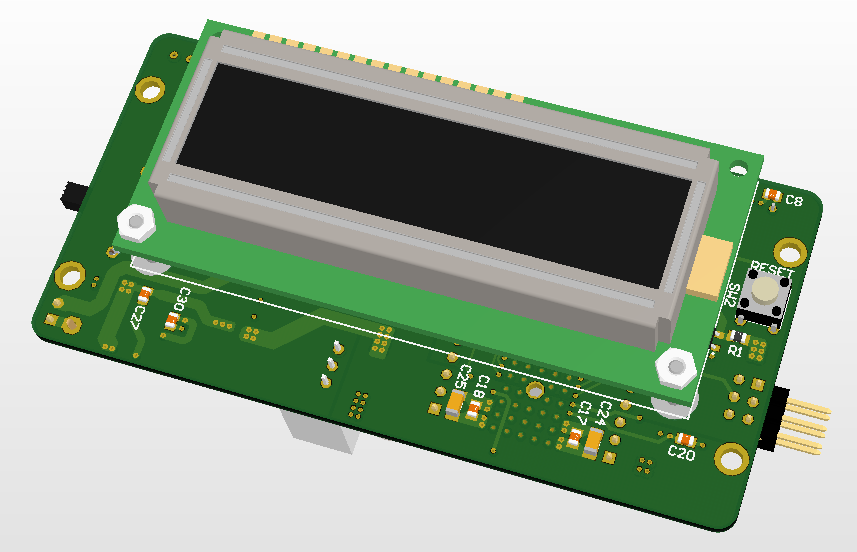

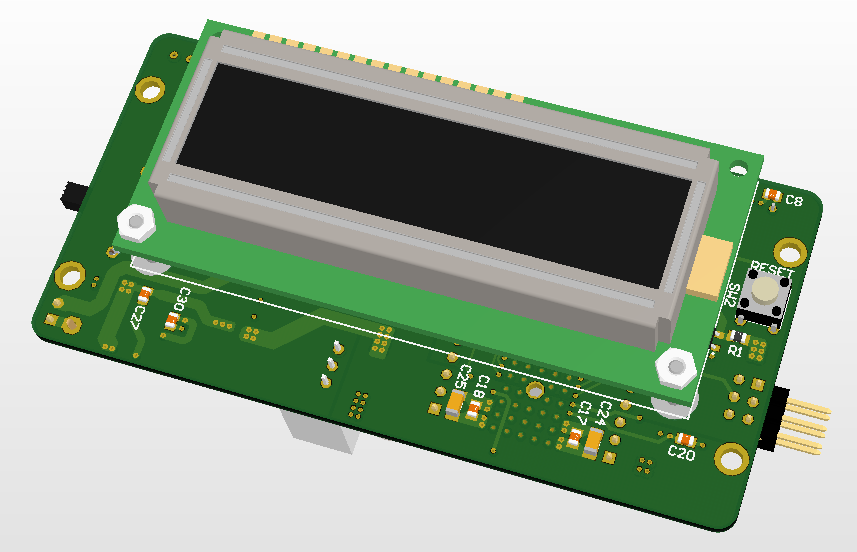

Портфоліо

Портфоліо

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

Відгуки

Зміни збережені

Показано з 1 по 5 із 50+ відгуків

$270,00 USD

C Programming

Engineering

Verilog / VHDL

Electrical Engineering

FPGA

A

•

$70,00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

•

$200,00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Arduino

FPGA

G

•

$150,00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+ ще 1

J

•

$80,00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+ ще 1

J

•

Досвід роботи

FPGA/Verilog/VHDL Developers

січ. 2018 - Цей час

Founder of FPGA4student. An experienced FPGA/Verilog/VHDL Engineer with more than 6 years experience and hundreds of FPGA projects in Verilog/ VHDL, Digital Logic/Circuit/System Design in LogiSim/CEDAR, and MIPS Assembly.

Expertise: Xilinx ISE, Vivado, Quartus, Modelsim, Logisim, CEDAR, Qtspim, MARS, PSpice, Altium, OrCAD, Proteus, Arduino.

Founder

лист. 2016 - Цей час

FPGA4student where shares free FPGA/Verilog/VHDL source code/ projects/ tutorials with EEE students.

Also offering FPGA/Verilog/VHDL Design/ Tutoring/ Consulting Services.

Experienced FPGA/Verilog/VHDL Engineer

серп. 2014 - Цей час

An experienced FPGA/Verilog/VHDL engineer with more than 6 years experiences on FPGA Design using Verilog/ VHDL, digital logic design LogiSim, Circuit design, MIPS Assembly, etc.

Освіта

IC Design Course

(1 year)

Bachelor of Engineering

(5 years)

Кваліфікація

IC Design Course Completion

Synopsys

2014

IC Design Course using Synopsys Design Tools

Odon Vallet scholarship

Prof. Odon Vallet and "Meeting Vietnam" Organization

2013

Scholarship for best performed students in central region of Vietnam in 2013

Intel Vietnam Engineering scholarship

Intel Vietnam

2012

Scholarship for top engineering students at DUT in 2011 and 2012

Публікації

A FPGA-Based Embedded Fingerprint Identification System

the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System on the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System

The University of Danang

A FPGA-Based Embedded Fingerprint Identification System

Зв'яжіться з Loi L. щодо вашої роботи

Авторизуйтесь, щоб обговорити деталі в чаті.

Верифікації

Сертифікати

Топ-навички

Пошук схожих фрілансерів

Переглянути схожі презентації

Запрошення успішно надіслане!

Дякуємо! Ми надіслали на вашу електронну пошту посилання для отримання безкоштовного кредиту.

Під час надсилання електронного листа сталася помилка. Будь ласка, спробуйте ще раз.

Завантажуємо для перегляду

Дозвіл на визначення геолокації надано.

Ваш сеанс входу закінчився, і сеанс було закрито. Будь ласка, увійдіть знову.